Emeraude Syfala HLS Grid5000 Conclusion

# First Syfala Workshop: Experimenting With the Faust to FPGA Compilation Flow Using Grid5000 Insa-Lyon 1/12/2023

Pierre Cochard, Maxime Popoff, Romain Michon, Tanguy Risset, Yann Orlarey, Matthieu Imbert and The Emeraude Team

Workshop

크 > < 크 >

| Workshop | Emeraude   | Syfala | HLS  | Grid5000 | Conclusion |

|----------|------------|--------|------|----------|------------|

| 00       | 000        | 0000   | 0000 | 000      |            |

| Table of | f Contents |        |      |          |            |

- Things to know about today

- 2 Emeraude Team

- 3 Syfala Project: Audio to FPGA Compilation

- 4 High Level Synthesis

- grid5000 for accessing Xilinx tools

- 6 Conclusion

| Workshop | Emeraude | Syfala | HLS  | Grid5000 | Conclusion |

|----------|----------|--------|------|----------|------------|

| ●○       | 000      | 0000   | 0000 | 000      |            |

| Table of | Contents |        |      |          |            |

- Things to know about today

- 2 Emeraude Team

- Syfala Project: Audio to FPGA Compilation

- High Level Synthesis

- 5 grid5000 for accessing Xilinx tools

- 6 Conclusion

э

| Workshop | Emeraude | Syfala | HLS  | Grid5000 | Conclusion |

|----------|----------|--------|------|----------|------------|

| ○●       | 000      | 0000   | 0000 | 000      |            |

|          |          |        |      |          |            |

## Syfala Recap: Challenges and Future Works

#### Program: (https://paw.grame. fr/#syfala)

- 09h00: Workshop Introduction (Tanguy Risset)

- 09h30: Introduction to Faust Langage (Yann Orlarey)

- 10h00: Hands-on Faust Language (Yann Orlarey)

- coffee Break

- 10h30: Introduction to FPGA (Maxime Popoff)

- 11h00: Introduction to Syfala-lab (Pierre Cochard)

- 11h30: Connecting to Grid5000 (Syfala Team)

- · 12h30: Lunch (Room 'projet A', same floor)

- · 14h00: Hands-on: Running Syfala Linux Workfkow

- 15h30: Advanced Syfala Use (Pierre Cochard, Maxime Popoff, Romain Michon)

- 16h30: Hands-on sand box: free experimental Audio to FPGA programming

- 18h00: End

Participants:

- 8 participants with various background

- +3 local attendees

Instructors:

- Pierre Cochard (github master)

- Maxime Popoff (Phd on Syfala)

- Yann Orlarey (Faust inventor)

- Romain Michon (embedded audio)

- Matthieu Imbert (grid5000)

ヘロト 人間 とくほとくほとう

• Tanguy Risset (head)

3

| Workshop | Emeraude<br>●oo | Syfala<br>0000 | HLS<br>0000 | Grid5000<br>000 | Conclusion |

|----------|-----------------|----------------|-------------|-----------------|------------|

| Table o  | f Contents      |                |             |                 |            |

- Things to know about today

- 2 Emeraude Team

- 3 Syfala Project: Audio to FPGA Compilation

- 4 High Level Synthesis

- 5 grid5000 for accessing Xilinx tools

- 6 Conclusion

э

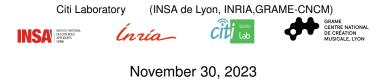

WorkshopEmeraudeSyfalaHLSGrid5000ConclusionWhy emeraude? and what for?

• Emeraude stands for:

Embedded Programmable Audio Systems

• New Research Team in Lyon (Mar. 2022) collaboration between The Grame institute and Citi research lab.

- Domains of expertise:

- Embedded Audio Systems

- Acoustics

- · Sound synthesis and effects

- Arithmetic for FPGA.

- Audio on FPGA

- Faust language development

#### A zoom on Emeraude's origins

・ロト ・ 理 ト ・ ヨ ト ・

3

| Table a  | f Contonts      |                |             |          |            |

|----------|-----------------|----------------|-------------|----------|------------|

| Workshop | Emeraude<br>000 | Syfala<br>●○○○ | HLS<br>0000 | Grid5000 | Conclusion |

- Things to know about today

- 2 Emeraude Team

- 3 Syfala Project: Audio to FPGA Compilation

- 4 High Level Synthesis

- 5 grid5000 for accessing Xilinx tools

- 6 Conclusion

ъ

Workshop<br/>ooEmeraude<br/>ooSyfala<br/>c ooHLS<br/>ooGrid5000<br/>oooConclusion<br/>oo

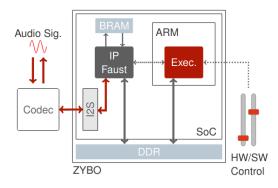

## Syfala development stages

Syfala original objective: reach smallest possible audio latency

First version (2020 no ARM control)

- 2021: Control on ARM (hardware or software-UART-based)

- 2021: Large memory handling (long delay lines)

- 2022: Ultra-low latency (11µs analog to analog)

- 2022: Parametric number of audio channels

- 2022: TDM I2S (up to 256 channels on Zybo Z10)

- 2023: Embedded Linux on ARM (Eth., Wifi, MIDI, etc.)

ヘロト 人間 ト ヘヨト ヘヨト

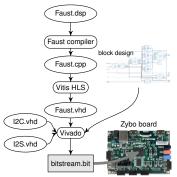

2023: C++ based compilation flow

э

Workshop

Emeraude

Syfala

HLS

Grid5000

Conclusion

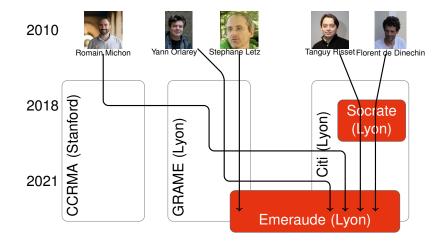

Syfala Compiler (2023) Conceptual View

#### Resulting audio system

Bare metal

With Linux

イロト 不得 とくほ とくほとう

ъ

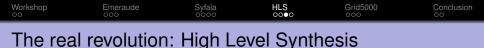

| Workshop | Emeraude<br>000 | Syfala<br>0000 | HLS<br>●000 | Grid5000 | Conclusion |

|----------|-----------------|----------------|-------------|----------|------------|

| Table o  | f Contents      |                |             |          |            |

- Things to know about today

- 2 Emeraude Team

- Syfala Project: Audio to FPGA Compilation

- 4 High Level Synthesis

- 5 grid5000 for accessing Xilinx tools

- 6 Conclusion

Workshop

Emeraude

Syfala

HLS

Grid5000

Conclusion

00

000

000

000

000

00

00

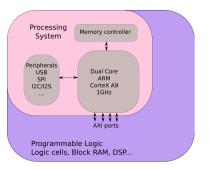

## Programming an FPGA Means ...

- many logic cells ("LUT")

- many small (≈ 24 bit) hard multipliers ("DSP blocks")

- many small (≈ 10 kBit) memories

- A SoC which includes a processing system (ARM@1GHz)

#### Zynq 7000 Processing System

イロト イポト イヨト イヨト

#### Example: Xilinx Zynq 7010 ( $\approx$ 50€): 2 ARM processor cores

+ **28k** logic cells + **80** DSP blocks + **60** 36kBit memory block ... running at **200 MHz**

э

A D b 4 A b

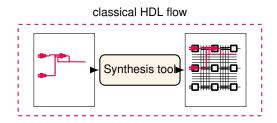

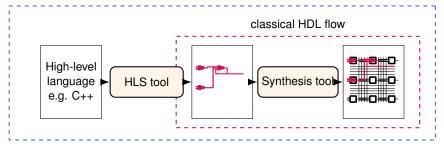

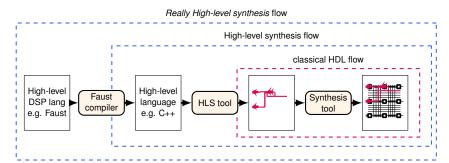

- Classic HDL flow: You don't program, you design a circuit

- with low-level languages such as VHDL or Verilog

- · with compilers called "synthesis tools" that can take hours

< ∃⇒

- · Classic HDL flow: You don't program, you design a circuit

- with low-level languages such as VHDL or Verilog

- · with compilers called "synthesis tools" that can take hours

- Since the 2010, HLS allows for FPGA programming in C/C++

- but you won't escape the synthesis tools

イロト イポト イヨト イヨト

#### Syfala real challenge: control HLS compilation

- Add a higher level to High Level Synthesis.

- · Use HLS source as a backend of a compiler (Faust compiler)

- Use HLS compiler (vitis\_hls) as a backend to Faust

- · Take advantage of parallel computation allowed by Faust

イロト イポト イヨト イヨ

| Workshop | Emeraude   | Syfala | HLS  | Grid5000 | Conclusion |

|----------|------------|--------|------|----------|------------|

| 00       | 000        | 0000   | 0000 | ●○○      |            |

| Table o  | f Contents |        |      |          |            |

- Things to know about today

- 2 Emeraude Team

- Syfala Project: Audio to FPGA Compilation

- 4 High Level Synthesis

- grid5000 for accessing Xilinx tools

- 6 Conclusion

→ Ξ → < Ξ →</p>

< 🗇 🕨

| Workshop | Emeraude<br>000 | Syfala<br>0000 | HLS<br>0000 | Grid5000<br>○●○ | Conclusion |

|----------|-----------------|----------------|-------------|-----------------|------------|

#### Syfala Infrastructure

what we need:

- Xilinx tools (80 GB):

- vitis\_hls (HLS)

- vivado (hardware synthesis)

- vitis (HW/SW system building)

- Linux building

- Linux sources

- qemu (cross compilation)

- Faust Compiler

・ 回 ト ・ ヨ ト ・ ヨ ト

what we need:

- Xilinx tools (80 GB):

- vitis\_hls (HLS)

- vivado (hardware synthesis)

- vitis (HW/SW system building)

- Linux building

- Linux sources

- qemu (cross compilation)

- Faust Compiler

How to run all that:

- A simple solution is a Linux container

- grid5000 allows us to:

- Use a distant Linux machine (at Nancy)

- Create a temporary account

- Import a Syfala container

- Run Xilinx tools remotely

イロト イポト イヨト イヨト

import bistream to flash on local Zybo boards

gros-22.nancy.g5K

Of course before all that you need to access Wifi...

э

ヘロン ヘアン ヘビン ヘビン

| Workshop | Emeraude   | Syfala | HLS  | Grid5000 | Conclusion |

|----------|------------|--------|------|----------|------------|

|          | 000        | 0000   | 0000 | 000      | ●○         |

| Table o  | f Contents |        |      |          |            |

- Things to know about today

- 2 Emeraude Team

- Syfala Project: Audio to FPGA Compilation

- 4 High Level Synthesis

- 5 grid5000 for accessing Xilinx tools

6 Conclusion

## Conclusion: next talk to come

- Yann Orlarey

- 09h30: Introduction to Faust Langage (Yann Orlarey)

- 10h00: Hands-on Faust Language (Yann Orlarey)

- Maxime Popoff

- introduction to FPGA

- Pierre Cochard

- Syfala-lab presentation

- 11h30: hands-on: connect to grid5000 and then lunch

# Questions?

https://github.com/inria-emeraude/syfala

・ 同 ト ・ ヨ ト ・ ヨ ト …